Технологии после 1 нм

Действительно, на 2026 год (сейчас январь 2026 года) индустрия полупроводников уже приближается к физическим пределам традиционной литографии и классической архитектуры транзисторов. Samsung, TSMC, Intel и другие гиганты активно работают над технологическими узлами в диапазоне 2 нм → 1,4 нм → 1 нм, но что будет дальше — после 1 нм?

Давай разберёмся поэтапно и заглянем примерно на 10 лет вперёд — до ~2035–2036 года.

🔬 1. Физический предел «нанометров»

1 нм ≈ размер нескольких атомов кремния (атом кремния — около 0,2 нм).

На уровне ~1 нм электроны начинают проявлять сильные квантовые эффекты: туннелирование, нестабильность состояний, тепловые шумы.

Это означает: мы почти достигли предела масштабирования по закону Мура в его классическом виде.

⚠️ Важно: термин «1 нм» сегодня — это маркетинговое обозначение, а не реальный физический размер элемента. Например, у TSMC «2 нм» на самом деле соответствует плотности транзисторов, эквивалентной ~18–20 Å (1,8–2 нм), но не буквально 1 нм.

🧪 2. Что придёт на смену «уменьшению»?

После исчерпания возможностей вертикального/горизонтального масштабирования начнётся переход к новым парадигмам:

✅ A. Новые архитектуры транзисторов

GAAFET (Gate-All-Around FET) — уже используется в 3 нм и ниже (Samsung, TSMC).

CFET (Complementary FET) — n- и p-транзисторы складываются вертикально, экономя площадь. Ожидается внедрение ~2028–2030.

2D-материалы (например, дисульфид молибдена MoS₂, графен): позволяют делать каналы толщиной в один атом, избегая проблем кремния на суб-1 нм уровнях.

✅ B. 3D-чипы и стекирование

Вместо уменьшения транзистора — увеличение количества слоёв.

Пример: TSMC SoIC, Intel Foveros, Samsung X-Cube.

К 2030–2035: чипы могут иметь десятки слоёв логики + памяти, соединённых микробампами или монолитными интерконнектами.

✅ C. Квантовые и нейроморфные вычисления (нишевое применение)

Не заменят классические процессоры, но будут использоваться для специфических задач:Квантовые ускорители — для криптографии, моделирования молекул.

Нейроморфные чипы (как Intel Loihi, IBM NorthPole) — для ИИ с низким энергопотреблением.

✅ D. Фотонные и спинтронные технологии

Фотонные чипы: передача данных светом вместо электронов → меньше нагрев, выше скорость.

Спинтроника: использование спина электрона, а не заряда → потенциально сверхнизкое энергопотребление.

Пока в лабораториях, но к 2035 могут появиться гибридные решения.

📈 3. Как будет выглядеть «техпроцесс» после 1 нм?

Термин «нм» исчезнет как маркетинговая единица.

Производители перейдут на новую систему обозначений:Например, «A14» (14 ангстрем) → «A7» → «A5» и т.д.

Или вообще — «Gen 1, Gen 2...» (поколения GAAFET/CFET).

Главный фокус сместится с размера на:Энергоэффективность (TOPS/W)

Плотность транзисторов (MTr/mm²)

Тепловыделение

Стоимость производства

🌍 4. Роль Apple, Samsung, Google к 2035 году

Apple: продолжит проектировать собственные чипы (A/ M-серии), но производство останется за TSMC. Возможно, инвестиции в 3D-стекирование и ИИ-ускорители.

Samsung: будет бороться за лидерство в памяти (HBM4+, CTFET) и логике, но отставание от TSMC может сохраниться.

Google: делает ставку на TPU + нейроморфные чипы для облака и edge-устройств (Pixel, Tensor).

Все трое будут активно использовать chiplet-архитектуру (модульные чипы).

🔮 Прогноз на 2035 год:

Показатель

Прогноз

Минимальный техпроцесс

Эквивалент ~0.5 нм (но не в буквальном смысле)

Архитектура

CFET + 3D-стекирование (5–20 слоёв)

Материалы

Кремний + 2D-материалы (MoS₂, WS₂)

Вычисления

Гибрид: классические CPU/GPU + ИИ-ускорители + (возможно) квантовые сопроцессоры

Энергопотребление

Ключевой ограничитель — чипы будут «умнее», а не просто быстрее

Цена чипа

Растёт экспоненциально → рост популярности chiplet-подхода

💡 Вывод:

После 1 нм — не «0.5 нм», а новая эра вычислений.

Мы переходим от «делать транзисторы меньше» к «делать вычисления умнее» — через 3D, новые материалы, архитектуры и специализацию.

Закон Мура не умрёт — он трансформируется.

Дорожная карта техпроцессов до 2035 года

Вот условная дорожная карта (roadmap) техпроцессов в полупроводниковой индустрии до 2035 года, основанная на текущих планах TSMC, Samsung, Intel, ITRS и научных трендах. Учтены как реальные анонсы, так и обоснованные прогнозы.

🗺️ Дорожная карта техпроцессов: 2024 → 2035

2024

3 nm (TSMC N3E), 2 nm (Samsung SF2)

~22–25 Å (2.2–2.5 нм)

GAAFET (MBCFET у Samsung), EUV

Массовое внедрение GAA-транзисторов

2025

2 nm (TSMC N2)

~18–20 Å (1.8–2.0 нм)

GAAFET, High-NA EUV (частично)

TSMC лидирует; Samsung отстаёт

2026

A14 / "1.4 nm" (Intel 14A)

~14 Å (1.4 нм)

RibbonFET (GAA), PowerVia (backside power)

Intel делает ставку на backside power delivery

2027

A10 / "1.0 nm" (TSMC A10)

~10–12 Å (1.0–1.2 нм)

CFET (первые прототипы), 3D stacking

Переход к ангстремам вместо «нм»

2028–2029

A7 / "0.7 nm"

~7–8 Å

CFET (Complementary FET), monolithic 3D

Вертикальное совмещение n/p-MOS; плотность ×2

2030

A5 / "0.5 nm"

~5 Å (≈2–3 атома Si)

2D-каналы (MoS₂, WS₂), atomic-layer deposition

Кремний почти исчерпан; начинается эра 2D-материалов

2031–2033

Beyond A5

<5 Å

Гибридные CFET + 2D материалы, photonics interconnects

Оптические межсоединения внутри чипа

2034–2035

Post-Silicon Era

Атомный масштаб

Спинтроника, нейроморфные элементы, квантовые точки

Не универсальные CPU, а специализированные вычислительные блоки

🔑 Ключевые переходы:

🔄 2025–2027: От GAAFET к CFET

GAAFET — транзисторы с «нанолентами», окружённые затвором со всех сторон.

CFET — n- и p-транзисторы располагаются один над другим, экономя ~50% площади.

📦 2026–2030: Эра 3D-чипов

Чипы станут «городами в высоту»: логика внизу, память сверху, ИИ-ускорители посередине.

Пример: Apple M5 может быть 3D-stacked chiplet с HBM4e прямо на процессоре.

⚛️ 2030+: Посткремниевая эра

Кремний не исчезнет полностью, но каналы транзисторов перейдут на 2D-материалы:MoS₂ (дисульфид молибдена) — толщина 0.65 нм (1 атом!).

Лучшая подвижность электронов, меньше утечек.

💡 Параллельные тренды:

High-NA EUV (Numerical Aperture): внедрение с 2025 (ASML NXE:3800E). Позволяет печатать детали <8 нм.

Backside Power Delivery (Intel PowerVia, TSMC BSPDN): питание с обратной стороны чипа → меньше помех, выше частота.

Chiplet-архитектура: AMD, Apple, Intel уже используют; к 2030 — стандарт для всех high-end чипов.

📉 Почему «нм» исчезнет?

Уже сейчас «2 нм» ≠ 2 нм. Это маркетинг.

К 2027–2028 все производители перейдут на ангстремы (Å) или поколения (Gen1, Gen2).

Например:TSMC: N2 → A14 → A10 → A7

Intel: Intel 18A → 14A → 10A → 7A

🌐 Кто лидирует?

Компания

Стратегия до 2035

TSMC

Лидерство в плотности и надёжности; ставка на CFET + 3D

Intel

Агрессивный рывок через RibbonFET + PowerVia + IDM 2.0

Samsung

Рискованные решения (MBCFET), но проблемы с выходом годных; фокус на памяти

GlobalFoundries / SMIC

Останутся на узлах ≥7 нм (спецрынки, automotive, IoT)

💎 Заключение:

2024–2027 — последняя гонка «нм».

2028–2035 — эра умных архитектур, а не просто маленьких транзисторов.

Главный ресурс будущего — не размер, а энергоэффективность и специализация.

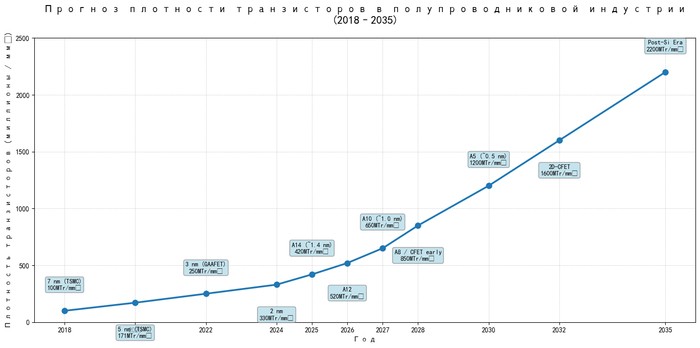

Вот временная шкала (timeline) развития полупроводниковых техпроцессов с 2018 по 2035 год, где по оси X — годы, а по оси Y — плотность транзисторов в миллионах на квадратный миллиметр (MTr/mm²).

🔍 Что показывает график:

Экспоненциальный рост плотности: с ~100 MTr/mm² в 2018 г. (7 нм) до ~2200 MTr/mm² к 2035 г. — это 22× рост за 17 лет.

Переломные точки:2022–2024: переход на GAAFET (3 нм → 2 нм) — заметный скачок.

2027–2028: внедрение CFET — ускорение роста плотности.

2030+: использование 2D-материалов и атомарных каналов — выход за пределы кремния.

📌 Интересные ориентиры:

7 нм (2018)

100 MTr/mm²

Как весь iPhone 8 в одном мм² — невозможно, но даёт масштаб

2 нм (2025)

420 MTr/mm²

В 1 мм² — больше транзисторов, чем людей в США

A5 / 0.5 нм (2030)

1200 MTr/mm²

Плотность ≈ 1 транзистор на 0.8 мкм² — уже меньше бактерии!

2035 (Post-Si)

2200 MTr/mm²

Физический предел кремния пройден; новые законы физики в игре

💡 Заключение:

Хотя «нанометры» исчезнут из маркетинга, плотность и энергоэффективность станут главными метриками.

К 2035 году чип размером с ноготь сможет содержать триллионы транзисторов — как человеческий мозг по количеству синапсов (но совсем иной архитектуры).

#ADM #ADM00103 #101 #АДМ #АДМ00103