С чего начать изучение FPGA. Часть 2. Детекторы фронта.

Приветствую уважаемые подписчики. Данный пост будет небольшой, но очень полезный. Сегодня я хочу познакомить вас с тремя маленькими, но архиважными схемами, которые достаточно часто применяются разработчиками. Данные схемы носят название детекторы фронта и применяются, как ни странно, для того, чтобы детектировать фронт импульса.

Например: есть какой-то длинный сигнал, и наша задача показать, что у нас сигнал изменился с 0 --> 1 или же с 1 --> 0.

Для этого давайте попробуем пропустить наш длинный сигнал через двух-разрядный сдвиговый регистр с параллельным выходом.

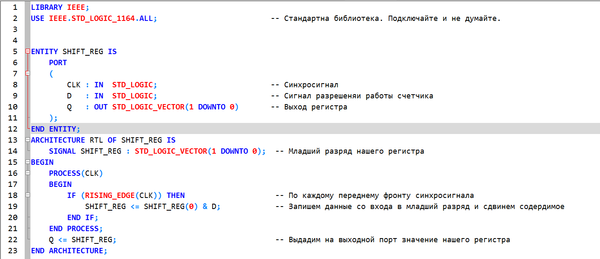

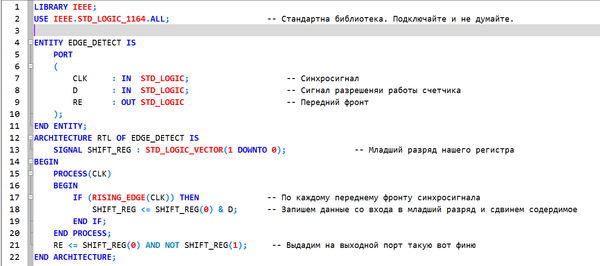

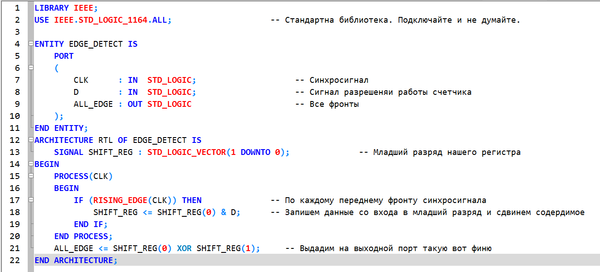

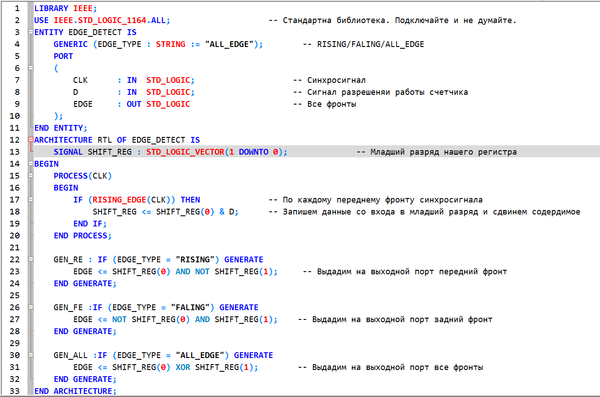

Опишем наш сдвиговый регистр на VHDL:

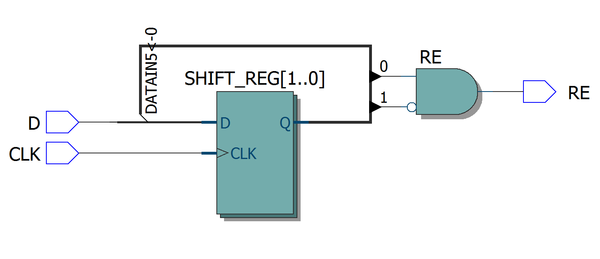

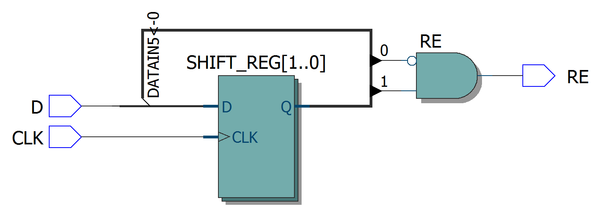

Вот как он у нас выглядит в RTL:

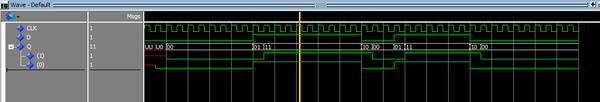

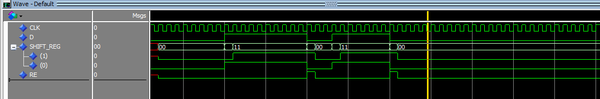

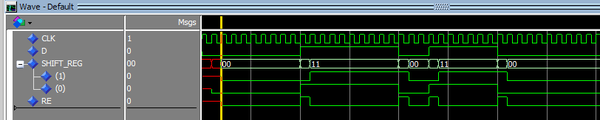

Надеюсь, вы представляете себе, как работает наш сдвиговый регистр? Если не представляете, то вот его временные диаграммы:

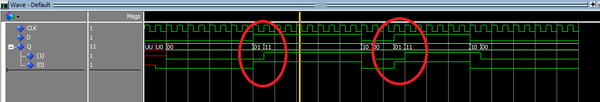

А теперь обратите внимание на места, выделенные красным:

Заметьте, каждый раз как у нас входной сигнал становиться равным логической единице, у нас в младший разряд записывается этот сигнал, а в старшем разряде в это время у нас записано прошлое состояние младшего разряда, т.е. лог.0.

Почему бы нам теперь не выдавать логическую единичку, если у нас в старшем разряде записан лог.0 , а в младшем лог.1 ?

Вот так вот будет выглядеть наша новая схема:

Вот её RTL представление:

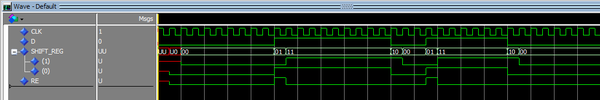

А вот временные диаграммы её работы:

Как видите – это то, что нам и было надо с самого начала!

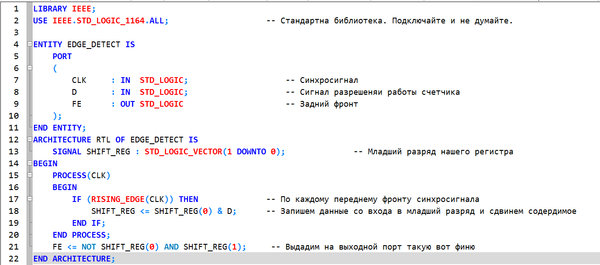

А если нам необходимо детектировать изменение сигнала с 1 --> 0 ?

То тут вообще все просто, нам достаточно немного переписать 21 строчку кода:

Вот так теперь будет выглядеть наша схема в RTL:

Ну и конечно вот наши времянки:

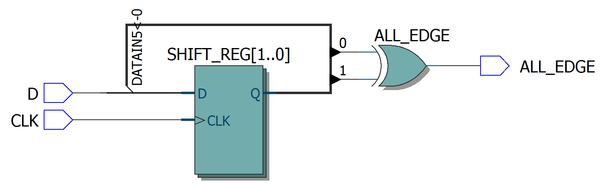

Последняя схема, сигнализирует о переднем и заднем фронте сигнала. Применяется не так часто, но для полноты картины я вам всё же её покажу.

Последняя схема получается, если поксорить наши регистры (от английского слова XOR, сложение по модулю 2):

Вот так вот она выглядит в RTL:

Ну и как всегда временные диаграммы:

Вот я вам и рассказал про три важные схемы, которые применяются для детектирования фронтов сигнала.

Но у этих трех схем есть один недостаток – это 3 разных файла, что очень неудобно.

Можно ли их как-то объединить в один ?

Кончено же можно !

Наши три файла легко описать в виде одного файла с параметрами, что, кстати говоря, является хорошим тоном при описании схем на HDL языках :

Теперь достаточно указать в параметрах тип детектируемого фронта, и схема автоматически будет выбираться та, которая нам нужна.

На сегодня это все. Спасибо за прочтение

P.S. Стоит ли мне дальше продолжать писать посты про основы работы с ПЛИС. У меня возникло ощущение, что никому кроме меня это нафиг не надо…