Продолжение поста «Технологии: "Alpha" история в фактах и комментариях»2

Часть 6. Крах DEC

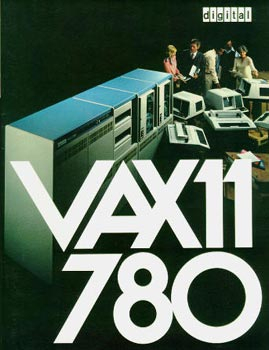

26 января 1998 компьютерный мир обошла новость, что находящаяся в критическом финансовом положенииDEC была куплена Compaq, и что сделка находится в процессе утверждения собраниями акционеров обеих компаний. Акционеры DEC ратифицировали соглашение 2 февраля 1998. Сумма сделки составила 9,6 млрд. долл. США, при ориентировочной рыночной капитализации DEC приблизительно в 7 млрд. долл. США. Начавшийся вскоре процесс интеграции подразделений DEC в структуры Compaq привёл к тому, что уже через полгода DEC окончательно прекратила своё существование (11 июня 1998 её акции перестали котироваться на Нью-Йоркской фондовой бирже). Стоит отметить, что переговоры между DEC и Compaq велись ещё с 1995, но сорвались в 1996 из-за позиции менеджмента DEC, настаивавшего на именно слиянии компаний, а не поглощении. Тем не менее, вполне закономерен вопрос: как могло так случиться, что огромная компания (по состоянию на 1989: почти 130 тыс. человек персонала, общий объём продаж около 14 млрд. долл. в год, то есть второй показатель по отрасли после IBM), с очень высоким исследовательским потенциалом и значительной производственной базой, была вынуждена продать себя крупному сборщику компьютерной техники из Техаса? Однозначного ответа на этот вопрос никто так и не дал, хотя причины называли разные. Об этом, и подробнее.

Давным-давно Кеннет Ольсен, основатель, президент и главный исполнительный менеджер DEC почти до самого её конца, сказал, что хорошие с инженерной точки зрения продукты продают себя сами. А следовательно в рекламе или ином продвижении не нуждаются. Ему также принадлежит изречение, что нет причины, из-за которой каждый захотел бы иметь компьютер у себя дома. Возможно, эти мысли оправдывали себя в "добрые старые" времена, когда компьютерная техника производилась в небольших количествах профессионалами для профессионалов и стоила довольно больших денег, но не в конце 20-го века, когда её продавали миллионами штук в год, и когда самый обыкновенный компьютер можно было собрать максимум за час времени при помощи отвёртки и деталей из ближайшего компьютерного магазина, и за сумму на порядок меньшую предыдущей. В конце концов, купить его целиком в том же магазине, ещё и с доставкой на дом. А если учесть, что покупать такой компьютер будет не менеджер с техническим образованием, прекрасно осознающий глубину смысла термина TCO (Total Cost of Ownership, совокупная стоимость владения), а некая тётя Маша или представитель подрастающего поколения Вовочка, в принципе не отличающие транзистор от резистора, то таких покупателей надо мотивировать явно не инженерными достоинствами потенциального приобретения. Ошибка #1.

Ещё в самом начале развития архитектуры Alpha высшим руководством DEC был допущен большой стратегический просчёт. Как известно, прототипы EV4 были продемонстрированы DEC на компьютерной конференции в феврале 1991. Среди присутствующих были инженеры Apple Computer, которые в то время занимались поиском новой процессорной архитектуры для будущих компьютеров компании, и возможности EV4 произвели на них впечатление. В июне того же года Джон Скалли (John Sculley), в то время главный исполнительный менеджер Apple, встретился с Кеннетом Ольсеном, и предложил использовать новый процессор DEC в будущих Маках. Ольсен отклонил предложение Скалли, мотивируя тем, что процессор ещё не готов для рынка, а архитектура VAX ещё не исчерпала себя. Через несколько месяцев было объявлено, что новые Маки будут использовать процессоры PowerPC от альянса Apple, IBM и Motorola. Позже Вильям Деммер (William Demmer), бывший вице-президент подразделений VAX и Alpha, ушедший в отставку в 1995, заявил в интервью Business Week от 28 апреля 1997: "Кен не хотел, чтобы будущее компании зависело от Alpha."Ошибка #2.

DEC сама производила как процессоры Alpha, так и чипсеты для них на своей фабрике в Хадсоне (Массачусетс), а также многочисленную периферию. Она также сама разрабатывала и изготовляла материнские платы, хотя и в довольно ограниченном ассортименте, и исключительно "десктопной" направленности (эти платы так и назывались,Evaluation BoardилиAlphaPC). Несмотря на то, что почти все без исключения Alpha-сервера DEC были многопроцессорными, ни одна из этих материнских плат SMP не поддерживала. Тем не менее, все материнские платы были выполнены на высоком техническом уровне, хотя и стоили недёшево, как и процессоры Alpha. Схемотехника этих плат была в свободном доступе, поэтому некоторые компании (Aspen, Polywell, Enorex, др.) производили их клоны; единственной компанией, разработавшей и производившей свои платы, былаDeskStation. В целом, можно смело утверждать, что приоритетом для DEC была продажа собственных рабочих станций и серверов, а не рынок комплектующих для тех же рабочих станций и серверов. С таким походом к делу можно как-то выжить, но нельзя победить в борьбе за рынок. Ошибка #3.

Несмотря на все попытки,DEC так и не смогла сделать цены на свою продукцию (акцентируя внимание на процессорах, чипсетах и материнских платах) доступными широким слоям потенциальных покупателей. Например, 266МГц и 300МГц EV5 по состоянию на начало 1995 стоили соответственно 2052 и 2937 долл. США в партиях по 1000 шт. -- непомерные цены, даже учитывая среднюю стоимость производства (модель MPR) в 430 долл. США за шт. В расчёте на один "попугай" SPECint92, EV5 стоил приблизительно в 2 раза дороже RISC-процессоров других производителей! При этом стандартный чипсет к нему, Alcor, продавался не в пример дешевле -- 295 долл. США в партиях по 5000 шт., хотя материнская плата на его основе (EB164, с 1Мб B-cache), вместе с процессором и 16Мб оперативной памяти (чего, кстати, было явно недостаточно для большинства задач, даже по меркам того времени), предлагалась по цене около 7500 долл. США. Ошибка #4.

Хотя Alpha была изначально объявлена "открытой архитектурой", консорциум по её развитию так и не был создан. Разработки велись усилиями DEC, иногда сообща с Mitsubishi. Получалось, что хотя собственно архитектура и была свободной де-юре, её основные разработки являлись очень даже закрытыми де-факто, так как патентовались соответствующим образом и подлежали платному лицензированию (если вообще подлежали), что мало способствовало успешному продвижению на рынке. Стоит отметить, что вскоре после выпуска EV4 руководство DEC предлагало лицензировать производство процессора Intel, Motorola, NEC, и Texas Instruments. Но эти компании имели свои разработки и были мало заинтересованы или незаинтересованные совсем в EV4, а потому отказались. Не исключено, что условия могли быть неприемлемы, или что-нибудь ещё. Ошибка #5.

Далее, даже самый быстрый компьютер без операционной системы и нужного программного обеспечения -- всего лишь дорогой источник шума и обогреватель окружающей среды. Свою Alpha-продукцию DEC позиционировала для Windows NT, Digital UNIX, и OpenVMS, причем именно в таком порядке приоритетности. Оно бы и ничего, но...

Windows NT-- это операционная система, изначально рассчитанная на пользователя, а не на программиста (так как не содержала никаких встроенных средств для разработки ПО), и поэтому сильно зависела от откомпилированного для неё ПО, и в первую очередь, коммерческого. А если смотреть фактам в лицо, то количество приложений, доступных для Alpha, отличалось в разы от аналогичного показателя для i386. Ситуацию в некоторой мере мог исправить FX!32, выпущенный в 1996 командой Антона Чернова (Anton Chernoff), отличный эмулятор и транслятор кода x86 в код Alpha, но от падения производительности как минимум на 40% не спасал, по сравнению с изначально откомпилированными под Alpha приложениями. Далее, драйвера как категория ПО; тут FX!32 ничем помочь не мог, и дела обстояли ещё хуже -- очень немногие производители сочли выпуск версий для Alpha целесообразным, поэтому приходилось рассчитывать, в основном, на Microsoft и DEC. В конце-концов, Windows NT (как 3.51, так и 4.0) была32-битной ОС, даже работая на 64-битной архитектуре Alpha, и поэтому не могла полностью раскрыть потенциал последней. Тем не менее, все эти оказии не мешали DEC продвигать свои Alpha-системы под слоганом "Рождён для работы с Windows NT" ("Born to run Windows NT"). В общем, такая ОС не должна была позиционироваться как основная для архитектуры Alpha, хотя собственно факт возможности её установки был большим плюсом для архитектуры. Ошибка #6.

OpenVMS и Digital UNIX (также известная как DEC OSF/1, и позднее как Compaq Tru64 UNIX), две надёжные и масштабируемые коммерческие операционные системы от DEC, так и не обрели широкой популярности из-за высоких цен (например, свыше 1000 долл. США за одну копию Digital UNIX 4.x в 1997), и, как следствие, закрытости исходного кода. Хотя с этими ОС были связаны и другие сложности (например, поддержка аппаратной базы была ещё более ограниченной, чем у Windows NT), но eсли хотя бы одна из этих ОС получила свободу, вместе с теми отличными инструментами для разработки ПО от DEC, то это могло серьёзно укрепить рыночные позиции архитектуры Alpha. Ошибка #7.

DEC никак не поддерживала бесплатные операционные системы с открытым кодом, хотя первая из них (NetBSD) была портирована на Alpha в 1995, а вслед за ней Linux, OpenBSD и FreeBSD. Это было, как минимум, странно, потому что и по сей день в этом сегменте архитектура Alpha пользуется широкой популярностью, и рыночная ценность вышеупомянутых ОС была очевидна даже на то время, постоянно увеличиваясь. Кроме того, эти ОС обеспечивали не худшее быстродействие по сравнению с коммерческими Digital UNIX и OpenVMS, и сопоставимую с Windows NT поддержку аппаратной части (намного лучшую с точки зрения дня сегодняшнего), и многие другие преимущества, которые можно ожидать от ПО с открытым кодом. Oшибка #8.

В список ошибок DEC можно было ещё включить игнорирование революции массовых и недорогих персональных компьютеров, чрезмерную диверсификацию бизнеса, и прочие менее значительные, но так как они не связаны непосредственно с архитектурой Alpha, можно подвести итоги. С точки зрения автора, DEC приложила множество усилий, чтобы заработать как можно больше денег при помощи архитектуры Alpha, но не приложила почти никаких усилий, чтобы помочь собственно архитектуре.

Из-за многочисленных неудач DEC в конце 1980-х и начале 1990-х, решением совета директоров в июле 1992 Ольсен был отстранён от руководства компанией, и на его место пришёл Роберт Палмер (Robert Palmer). В 1994 по его инициативе была проведена полная реорганизация менеджмента компании, которая из "матричной" (когда функционально разные отделы компании тесно взаимодействовали между собой при принятии решений) трансформировалась в традиционную "вертикальную" (с чётко выраженными полномочиями и обязанностями от самого верха компании и до самого низа). Чистые убытки DEC за период с 1991 по 1994 составили свыше 4 млрд. долл. США, из них 2 млрд. только с июля 1993 по июль 1994 (учитывая 1,2 млрд. на реорганизацию), а количество персонала сократилось до 85 тыс. чел. Согласно программе Палмера, следовало избавиться от подразделений, не являющихся приоритетными для компании, и с этого момента началась глобальная распродажа. В июле 1994 за 400 млн. долл. США было продано Quantum подразделение по разработке и производству дисковых и ленточных накопителей (Storage Business Unit), вскоре после провала первых моделей жёстких дисков с тонкоплёночным покрытием пластин (RA90 и RA92), слишком поздно вышедших на рынок из-за недоработок при проектировке, и не выдержавших конкуренции. В августе 1994 за 100 млн. долл. США было продано Oracle подразделение баз данных (Database Software Unit), и тогда же за 140 млн. долл. США была продана 7,8% доля в итальянской Olivetti. В ноябре 1997 была подписана сделка о продаже Cabletron за 430 млн. долл. США подразделения сетевых решений (Network Product Business Unit).

Kонец DEC был довольно громким. В мае 1997 она подала в суд на Intel, обвиняя последнюю в нарушении 10 своих патентов на архитектуру Alpha при проектировании процессоров Pentium, Pentium Pro и Pentium II. В сентябре 1997 Intel ответила встречным иском, обвиняя DEC в нарушении 14 патентов при разработке процессоров Alpha. В конце-концов, 27 октября 1997 мир был подписан: обе компании отзывают свои претензии, DEC предоставляет Intel производственные права на весь спектр своей продукции (кроме сегмента Alpha), и соглашается поддерживать будущую архитектуру IA-64, а Intel выкупает у неё за 625 млн. долл. США фабрику в Хадсоне вместе с проектными центрами в Иерусалиме (Израиль) и Остине (Техас), и берётся за производство процессоров Alpha в будущем. Кроме того, был подписан договор о взаимном кросс-лицензировании патентов сроком на 10 лет. Сделка была завершена 18 мая 1998; к тому времени Compaq уже адаптировала в свои структуры основные подразделения DEC, включая 38 тыс. сотрудников (по сравнению с 32 тыс. у самой Compaq до поглощения), хотя значительная их часть всё же была сокращена в самом ближайшем будущем.

Стоит упомянуть, что незадолго до конца DEC, а также вскоре после этого, многие ведущие инженеры, которым DEC была обязана своим могуществом, ушли к другим работодателям: Деррик Мейер (Derrick Meyer) ушёл в AMD создавать K7; туда же, но архитектором K8, ушел Джеймс Келлер (James Keller); Дэниел Лейбхольц (Daniel Leibholz) ушёл в Sun разрабатывать UltraSPARC V; также уволился Ричард Сайтс, один из ведущих разработчиков архитектуры Alpha на протяжении всего времени её существования. В этом плане Intel повезло ещё меньше: доставшаяся ей от DEC архитектура StrongARM осталась почти без разработчиков, так как никто из ведущих инженеров, проектировавших StrongARM-110, а именно Дэниел Добберпуль, Ричард Витек, Грегори Хеппнер (Gregory Hoeppner) и Лайэм Мэдден (Liam Madden), не пожелал перейти на работу в Intel, а команда разработчиков StrongARM второго поколения, работавшая под руководством Витека в Остине, уволилась в полном составе, так что Intel пришлось разрабатывать ядро в буквальном смысле с нуля, усилиями своих инженеров, до этого разрабатывавших i960.

Часть 7. EV6, EV67, EV68C, EV68A

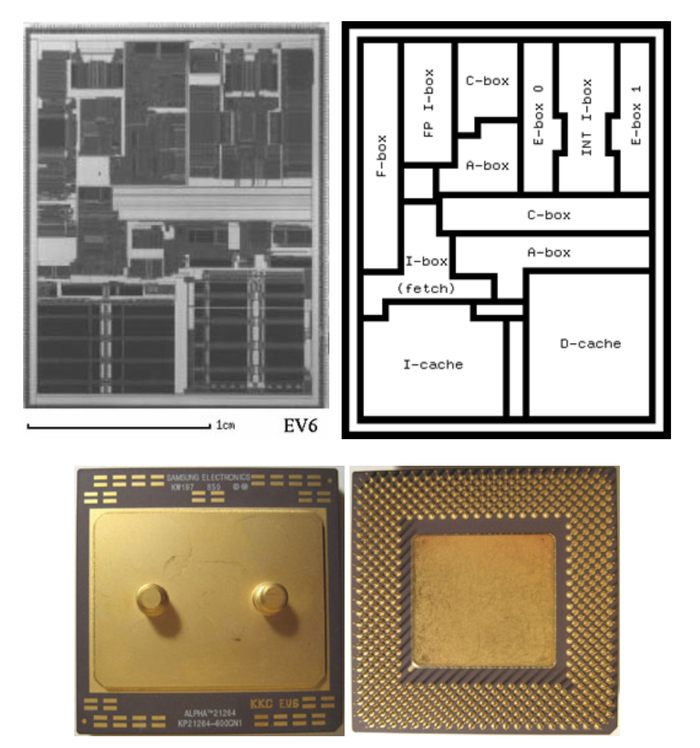

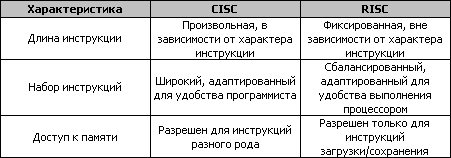

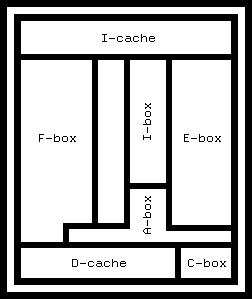

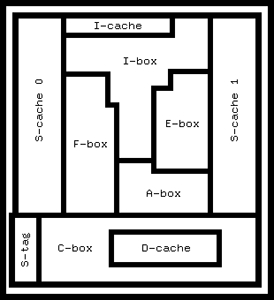

Хотя процессор 21264 (EV6) был разработан в DEC, и первая информация о нем была опубликована в октябре 1996 на Microprocessor Forum, окончательное воплощение в кремнии датируется февралём 1998, когда DEC уже была в процессе ликвидации. Собственно процессор представлял собой довольно существенный шаг вперед по сравнению с EV5, во многих аспектах революционный. Одним из основных нововведений было внеочередное исполнение (out-of-order execution) инструкций, повлёкшее за собой фундаментальную реорганизацию ядра, и снизившую зависимость основных функциональных устройств от пропускной способности кэшей и оперативной памяти. EV6 мог переупорядочить на лету до 80 инструкций, а это значительно больше, чем у других конкурентных разработок (к слову, архитектура Intel P6 предусматривала внеочередную обработку до 40 [микрокоманд], HP PA-8x00 -- до 56, MIPS R12000 -- до 48, IBM Power3 -- до 32, а PowerPC G4 -- до 5; разработанный к тому времени Sun UltraSPARC II переупорядочивание команд не поддерживал). Внеочередное исполнение дополнялось техникой переименования регистров (register renaming), и для этого в ядро было встроено дополнительно 48 целочисленных и 40 вещественных физических регистров (количество логических, то есть программных, осталось неизменным).

Количество целочисленных конвейеров было увеличено до 4 (организованных в 2 кластера), но функционально они были несколько неоднородны: 2-й конвейер мог выполнять операции умножения (7 тактов на инструкцию) и сдвига (1 такт), а 4-й -- MVI (3 такта) и сдвига; кроме того, все 4 конвейера поддерживали отработку элементарных арифметических и логических операций (1 такт). Каждый кластер располагал своим файлом целочисленных регистров (как упомянуто выше, на 80 записей), содержимое которых было идентично (синхронизировалось). 1-й и 3-й конвейеры также выполняли некоторые функции A-box, рассчитывая виртуальные адреса для операций загрузки/сохранения. Собственно A-box работал с I-TLB и D-TLB (каждый на 128 записей), очередями загрузки и сохранения (каждая по 32 команды), и 8 64-байтными буферами (miss address file) для операций с B-cache и основной памятью. Вещественные конвейеры также были функционально различны: 1-й поддерживал операции сложения (4 такта), деления (12 тактов для одинарной точности и 15 тактов для двойной), вычисления квадратного корня (15 и 30 тактов), а 2-й -- только умножения (4 такта). Между прочим, блок вычисления квадратного корня и соответствующие инструкции были нововведениями для архитектуры Alpha. Декодер, как и прежде в EV5, подавал до 4 инструкций за такт, а планировщик распределял их в 2 очереди: на целочисленные конвейеры (I-queue, 20 команд), и на вещественные конвейеры (F-queue, 15 команд). Кроме вычисления квадратного корня, были добавлены инструкции предварительной выборки, а также команды для переноса данных между целочисленными и вещественными регистрами.

Структура C-box подверглась значительным изменениям: теперь он работал только с 2 уровнями кэш-памяти. Интегрированный в ядро L1 состоял из 64Кб I-cache и 64Кб D-cache, оба с 2-канальной ассоциативностью и 64-байтными строками, причем D-cache работал в режиме обратной записи, хотя всё так же дублировался в B-cache. Из-за значительных размеров и усложнённой организации задержки D-cache при чтении/записи были увеличены до 3 тактов (в/из целочисленного регистра) и 4 тактов (в/из вещественного регистра). D-cache так и остался двухпортовым, но, в отличие от EV5, он уже не состоял из 2 одинаковых частей, синхронизированных по записи, а был просто заведён на удвоенной частоте. Внешний B-cache, размером от 1Мб до 16Мб с прямым отображением и обратной записью, использовал независимую 128-битную двунаправленную шину данных (с дополнительными 16 битами для ECC), а также независимую 20-битную однонаправленную шину шину адреса; набирался на микросхемах LW SSRAM (late-write, с отложенной записью), а позднее и DDR SSRAM (double data rate, с удвоенной скоростью передачи данных); частота B-cache программировалась (от 2/3 до 1/8 частоты ядра), и, в отличие от предыдущих поколений процессоров Alpha, собственно B-cache не был опциональным. Системная шина данных была только 64-битной (с дополнительными 8 битами для ECC), двунаправленной, но использовала технологию DDR. Системная шина адреса была 44-битной, физически представленная в виде двух 15-битных однонаправленных каналов, без поддержки DDR. 15-битная системная шина управления DDR также не поддерживала. Был изменён базовый принцип работы системной шины, которая теперь стала выделенной (вместо разделяемой), то есть каждый процессор имел свой путь к чипсету.

Блок предсказания ветвлений был полностью переработан. Теперь он был организован по 2-уровневой схеме: с локальной историей переходов (local history table, 1024 записи с 10-битными счетчиками) и локальным предсказателем (local predictor, 1024 записи по 3 бита), а также с глобальным предсказателем (global predictor, 4096 записей по 3 бита) и 12-битным "путем истории" (history path). Оба алгоритма работали независимо, и если локальный отслеживал каждый отдельный условный переход, то глобальный -- последовательности переходов. Общий предсказатель ветвлений анализировал результаты обоих алгоритмов, и делал выводы в виде отдельной таблицы выборочного предсказателя (choice predictor, 4096 записей по 2 бита), на основе которой выводились предпочтения при расхождении локальных и глобальных прогнозов. Такой кооперативный метод позволял добиться лучших результатов, чем применение любого из подходов в отдельности.

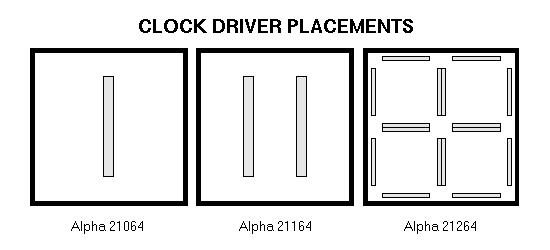

При разработке EV6, учитывая большое число и сложность организации взаимодействия функциональных устройств, была полностью переработана схема расположения генераторов тактовых частот. Более равномерное распространение тактового сигнала позволило ядру работать на частотах, равных частотам куда более простого ядра EV56, при использовании того же техпроцесса. В общем, потребляемая частотными генераторами мощность составляла для EV6 около 32% от общего потребления ядра; для сравнения, у EV56 этот показатель был около 25%, у EV5 -- около 37%, у EV4 -- около 40%.

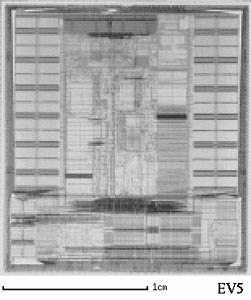

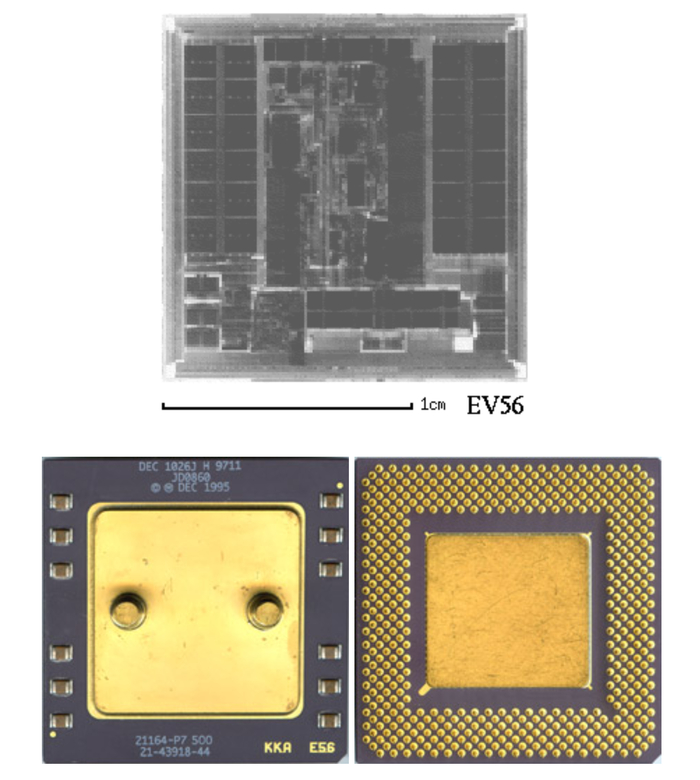

Физически EV6 производился по той же 6-слойной 0,35µ CMOS6 технологии, что и EV56, состоял из 15,2 млн. транзисторов (из них около 9 млн. на I-cache, D-cache, и предсказатели переходов), имел площадь ядра в 314 кв.мм., и был рассчитан на рабочее напряжение от 2,1В до 2,3В. Тактовые частоты составляли от 466МГц до 600МГц (TDP прибл. от 80Вт до 110Вт). Форм-фактор: PGA-587 (Pin Grid Array).

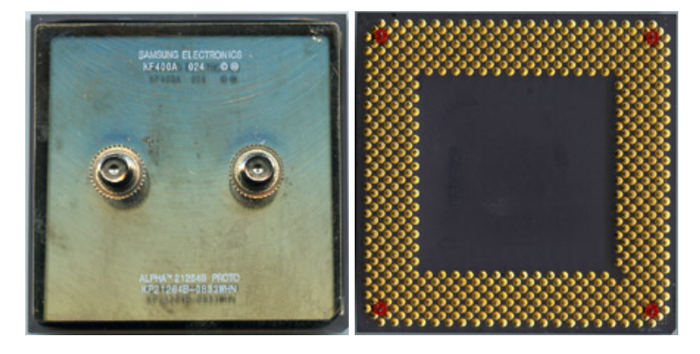

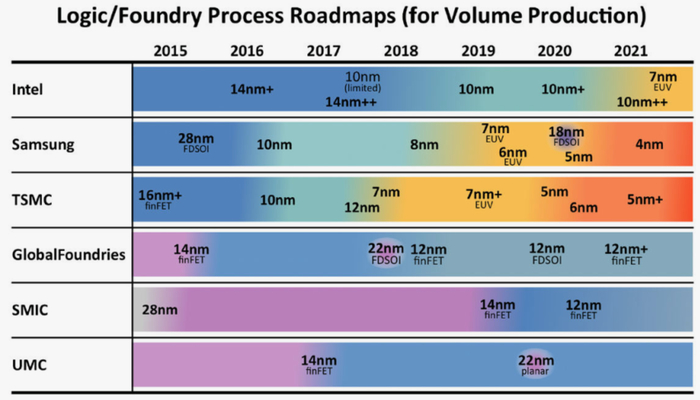

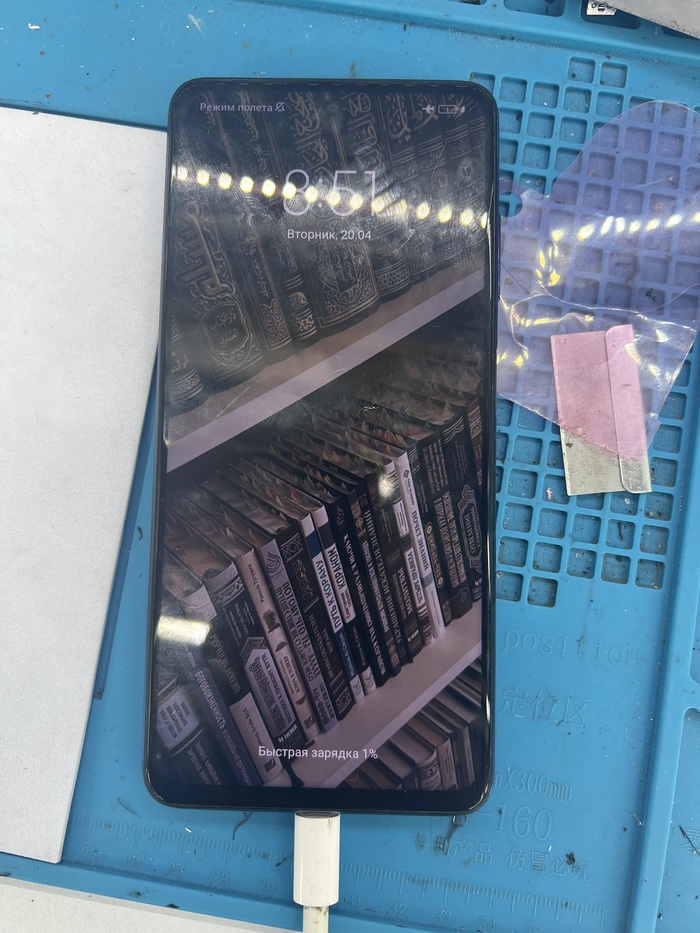

В конце 1999 на рынок вышел 21264А (EV67), выполненный по 0,25µ CMOS7 техпроцессу от Samsung, с площадью ядра в 210 кв.мм., и пониженным рабочим напряжением в 2,0В. Никаких архитектурных изменений по сравнению с EV6 не наблюдалось. Тактовые частоты составили от 600МГц до 833МГц (TDP прибл. от 70Вт до 100Вт), что позволило Alpha вернуть лидерство на целочисленных операциях, незадолго до этого утраченное в пользу процессоров Intel и AMD.

В начале 2000 появились первые процессоры 21264B (EV68C), на этот раз от IBM, по 0,18µ CMOS8 техпроцессу с использованием медных проводников. Несмотря на прежнее отсутствие архитектурных изменений, многообещающая технология позволила поднять тактовые частоты сразу до 1250МГц. В 2001 Samsung смог наладить производство 21264B (EV68А) по своему 0,18µ техпроцессу, но с алюминиевыми проводниками, сократив площадь ядра до 125 кв.мм., и уменьшив напряжение питания до 1,7В, что позволило вывести тактовые частоты в диапазон от 750МГц до 940МГц (TDP прибл. от 60Вт до 75Вт).

В разных источниках проскакивали упоминания о 21264C и 21264D, с кодовыми именами EV68CB и EV68DC, выпускавшимися IBM по той же технологии, что и EV68C, и с теми же частотными характеристиками, поэтому их можно рассматривать как частные варианты последнего. Единственным существенным отличием было использование нового форм-фактора, "безногого" CLGA-675 (Ceramic Land Grid Array) вместо PGA-587.

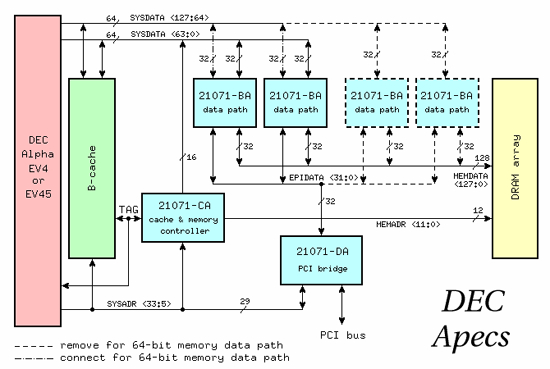

Для процессоров серии 21264 было спроектировано 2 чипсета: DEC Tsunami (21272; он же Typhoon) и AMD Irongate (AMD-751), хотя их могло бы быть значительно больше, ввиду того, что и 21264, и Athlon использовали почти одинаковую системную шину (она была лицензирована AMD ещё у DEC).

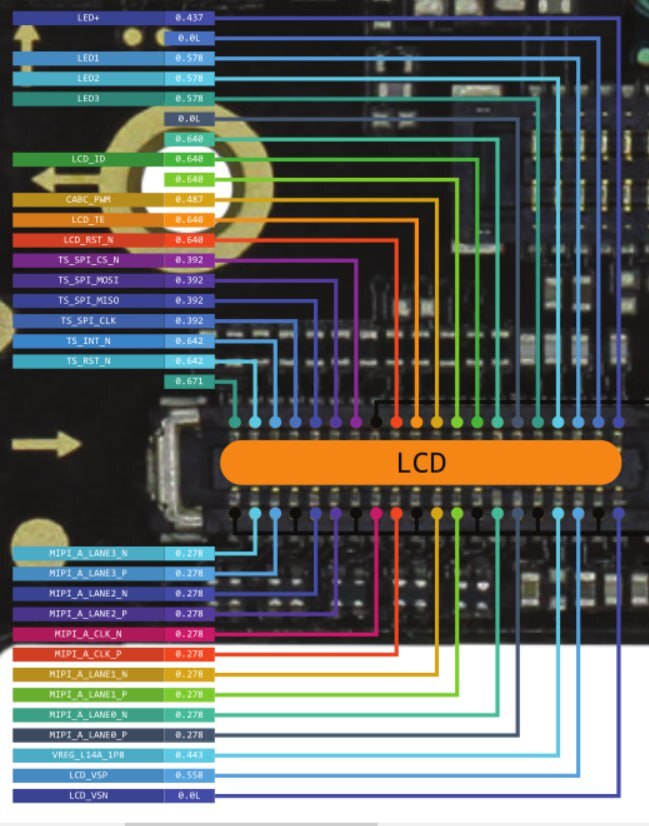

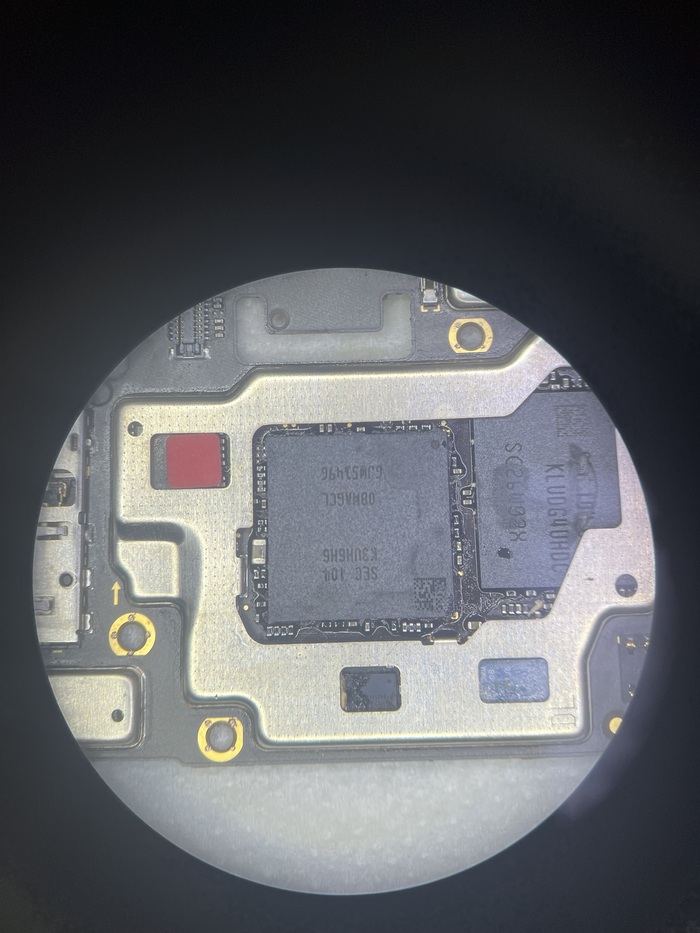

DEC Tsunami был чипсетом повышенной масштабируемости. На его основе проектировали как однопроцессорные, так двухпроцессорные и четырехпроцессорные системы, с разрядностью шины памяти от 128 до 512 бит (SDRAM ECC registered, 83МГц), поддержкой как одной, так и нескольких шин PCI (64-бит, 33МГц). Такой гибкости удалось достичь благодаря разделению чипсета на отдельные компоненты: контроллеры системной шины (C-chips, по одному на каждый процессор), контроллеры шины памяти (D-chips, по одному на каждые 64 бита ширины шины), и контроллеры шины PCI (P-chips, по одному на каждую требуемую шину). Поэтому ничего удивительного, что в некоторых системах (например, AlphaPC 264DP) чипсеты состояли из 12 микросхем...

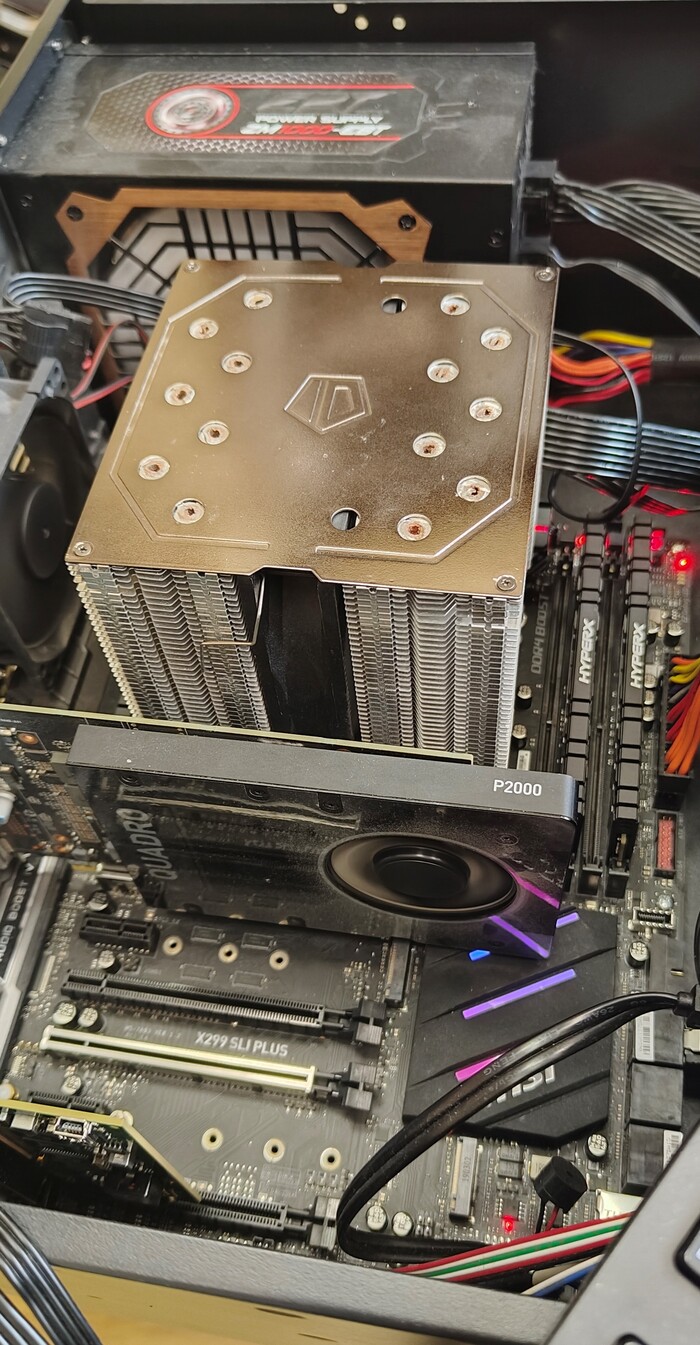

Хотя AMD Irongate разрабатывался изначально как северный мост для материнских плат, предназначенных для процессоров Athlon, его также использовали в некоторых материнских платах для Alpha (например, UP1000 и UP1100). Так как он был одночиповым решением, то стоил намного дешевле DEC Tsunami и отличался существенно более низким энергопотреблением. Однако, его возможности не соответствовали потенциалу 21264 из-за отсутствия поддержки многопроцессорности и слишком узкой шины памяти (64-бит, SDRAM ECC unbuffered, 100МГц). Тем не менее, Irongate был первым чипсетом для Alpha с поддержкой шины AGP. И последним.

В виду ограничения количества символов в статье

Продолжение следует...